Abstract

The effectiveness of sensor networks depends critically on efficient power management of the sensor nodes. Dynamic voltage frequency scaling (DVFS) and dynamic power management (DPM) have been proposed to enable energy-efficient scheduling for real-time and embedded systems. However, most power-aware scheduling algorithms are designed to deal with only those cases in which the task execution time is determined solely by the clock frequency of the processor. In this study, we propose an extended task execution model that is appropriate for the sensor nodes and an algorithm that determines the optimal clock frequency for a node's processor. We analyze the extended model and verify that our algorithm calculates the clock frequency that optimizes energy savings while satisfying the timing constraints.

1. Introduction

A typical sensor network consists of multiple sensor nodes and wireless networks that connect these nodes. Each sensor in a sensor network runs on a battery with a limited power supply [1]. Hence, it is considered critical for the sensor node to operate in an energy-saving manner. Numerous approaches have been reported recently for saving the sensors’ energy [2, 3].

Each sensor node is composed of units for sensing, processing, radio frequency (RF) transmission, and battery power supply. A typical sensor executes real-time applications with timing constraints; the application periodically operates sensing units, processes the collected data, and transmits the processed data to the wireless network; thus, the challenge at the sensor node is to finish the above tasks with minimal energy expenditure while satisfying the timing constraints. There are real-time scheduling algorithms that are designed to address energy issues; among them, DVFS [4] and DPM [5, 6] are the most widely used schemes in the field.

DVFS is a technique in which the clock frequency and the operating voltage of a processor are adjusted during the execution. A processor operates at different clock frequencies depending on the core voltage. Reducing the core voltage and the clock frequency not only reduces energy use, but also reduces execution speed; thus, in any reduction scheme of this type there is a limit on the energy savings that can be realized without violating the timing constraints.

Real-Time DVFS technology has also been developed to exploit DVFS while also addressing the issue of timing constraints. Various other approaches have been reported in the literature to exploit DVFS, including the use of various models to describe the relevant tasks and systems [7–9].

The DPM technique functions differently, switching a device into a sleep mode when there is no task to execute. A device consumes minimal energy while in sleep mode but is also inactive, and waking the device typically entails a certain delay. This issue should be considered when developing a scheduling algorithm that not only uses sleep mode but also needs to guarantee real-time responsiveness. Benini et al. [10] have studied the question of when to switch a device into sleep mode in real-time scheduling.

Recently, Devadas and Aydin [11] and Zhao and Aydin [12] studied the interplay of DVFS and DPM for a real-time embedded system. They analyzed the combined use of DVFS and DPM for a real-time application that uses devices. However, these approaches employ an execution model in which the execution time of a real-time task depends only on the clock frequency of the processor, which means that every device is impacted by the clock frequency. In practice, there are devices that do not depend on the clock frequency. We argue that an extended task execution model should be studied that takes both the processor and the devices into account.

In this study, we propose an extended energy model in which both of clock-dependent and clock-independent task executions are considered and present analysis results on this model. In addition, we provide an algorithm for calculating the clock frequency of the processor that optimizes the system's energy consumption; this algorithm was developed considering the interplay of DVFS and DPM for the extended model. This paper is extended from our preliminary work [13] for the nodes of sensor network.

The rest of this paper is organized as follows. Section 2 describes the system architecture of a sensor node. Section 3 proposes an extended model that considers both the clock-dependent and clock-independent task executions. In Section 4, we analyze the extended model and derive an algorithm to determine the optimal clock frequency; that is, the frequency that minimizes energy consumption while satisfying the timing constraints. Section 5 presents simulation results and analysis. We summarize the paper and suggest future work in Section 6.

2. Sensor Node Architecture

Figure 1 shows the system architecture of a typical sensor node with multiple sensor units.

Architecture of the sensor node.

As shown in Figure 1, a sensor node consists of a microcontroller unit (MCU), a RF Unit (RFU), a battery, and multiples sensor units (SUs). The analog signal detected by each SU is translated into digital data after being processed by the analog digital convertor (ADC) of the MCU. Hence, the resources such as CPU, memory, ADC, and RFU are shared by multiple SUs. The control unit controls the other components within the MCU.

It should be noted that each SU is designed to operate at a fixed frequency that is typically determined by the system designer; hence, the sensor unit is a system clock-independent device. In addition, the RFU operates at yet another frequency and depends neither on the clock frequency of the CPU nor on that of the sensor unit.

3. System Models

In this section, we present models for the task execution, the device's operation, and the system's energy consumption. The task execution model is designed to consider the different clock frequencies of the processor and the device. We normalize the clock frequencies of the processor and the device into the range of

3.1. Task Execution Model

Recent studies on the interplay of DVS and DPM for a real-time embedded system [11, 12] proposed the following model for task execution:

By using this model, we can calculate a task's execution time by a processor with the clock frequency f. In the equation,

However, the above model does not consider the case in which the execution time also depends on the clock frequency of the device. We present an extended model for considering the frequencies of both the processor and the device as shown in (2). In this equation,

Each

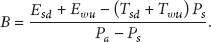

Equation (3) shows how to determine

Equations (4) shows that

3.2. Device Model

In this paper, we assume that the devices attached to the system support both DVFS and DPM. There are two device modes: active mode and sleep mode. In active mode, the device is ready to process requests, while in sleep mode, the device goes into a low-power mode and cannot process requests. In addition, we assume that the device is in an active mode at the beginning of the task and stays in this the mode until the task execution ends; this is typically referred to as intertask device scheduling. The following list gives various notations for device parameters:

The break-even time B represents the minimum duration of the sleep mode that will compensate for the added power consumption incurred in changing between the active and sleep mode. Devadas and Aydin [11] calculated the break-even time as shown in (6) and we adopt this calculation in our extended execution model:

3.3. Energy Model

The system energy E is partitioned into the static energy

4. Optimal Frequency Decision in SUs

In order to simplify the discussion, we assume that a sensor node is equipped with a sensing unit that runs at a fixed frequency. The following equation represents an extended energy model for this scenario:

The analysis of our energy model is illustrated in the following sections. In addition, we discuss how to determine the optimal frequency that minimizes the sensor node's energy consumption. Note that the analysis result is very similar to [11] because our model is extended from theirs. In the following, we shall refer the left and the right areas based on

4.1. Minimum Energy Consumption Frequency Decision in Area α

In area α, the device is never switched into the sleep mode during its idle time because the duration of sleep mode would be shorter than the break-even time. Therefore, the energy consumption of the device is a constant value

Note that the execution of the task is finished exactly at its deadline when

Figure 2 shows the energy consumption trend in area α. The energy consumption increases monotonically as a function of frequency. Hence,

Energy consumption in area α.

4.2. Minimum Energy Consumption Frequency Decision in Area β

In area β we need to consider the tradeoff between the energy consumption by the processor and the device with respect to the clock frequency. The energy model can be obtained as follows:

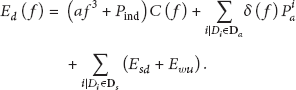

Equation (10) is strictly convex for

Energy consumption in area β.

Solving the quartic formula yields four values. The derivative of our energy model consists of a second-order term that is positive infinite at

Two Solutions of (11):

We can choose a clock frequency that minimizes the energy consumption in area β as that frequency that minimizes energy consumption for

if

if

if

4.3. Optimal Frequency Decision

Now, we can choose a frequency that optimizes the energy consumption by considering the results from both areas. The difference in the optimal energy consumption of each area is denoted by

Algorithm 1 shows an algorithm that derives the optimal clock frequency for a sensor node. After calculating the optimal frequency for each area using (10), we choose the optimal clock frequency between the two.

(1) (2) (3) (4) (5) (6) (7) (8) (9) (10) (11) (12) (13) (14) (15) (16) (17) (18) (19) (20) (21) (22)

5. Simulation Results

In this section we evaluate our algorithm in various scenarios. Throughout this section, we assume a real-time task with

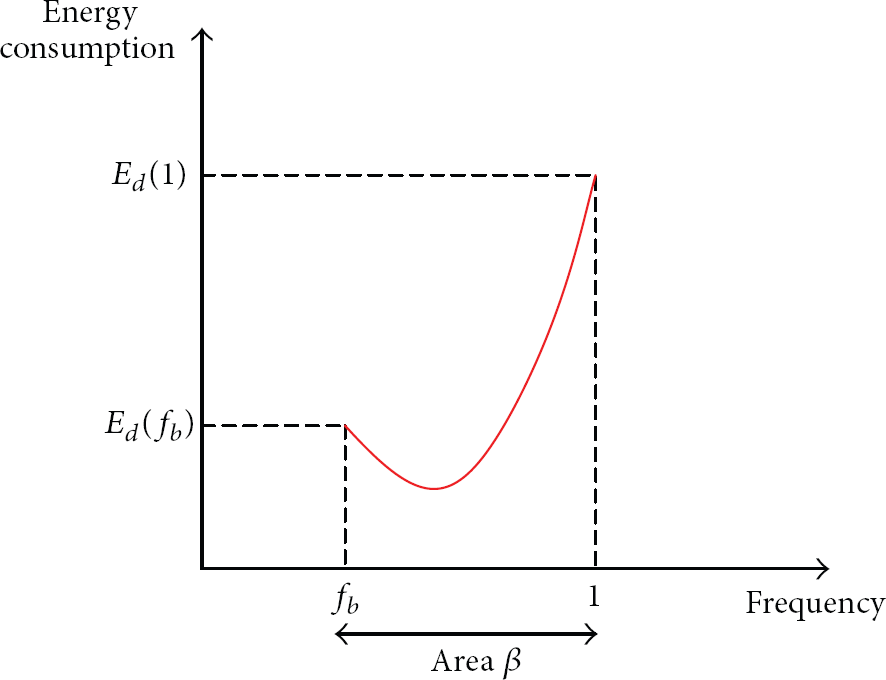

Figure 4 shows that the previous approach fails to handle the case in which the execution time of the task is not determined solely by the clock frequency. In the figure, the clock frequency dependency ∅ changes from 0.1 to 1, and only when the entire system depends on the clock frequency, that is,

Optimal clock frequencies for various ∅, as determined by a previous approach and the proposed approach.

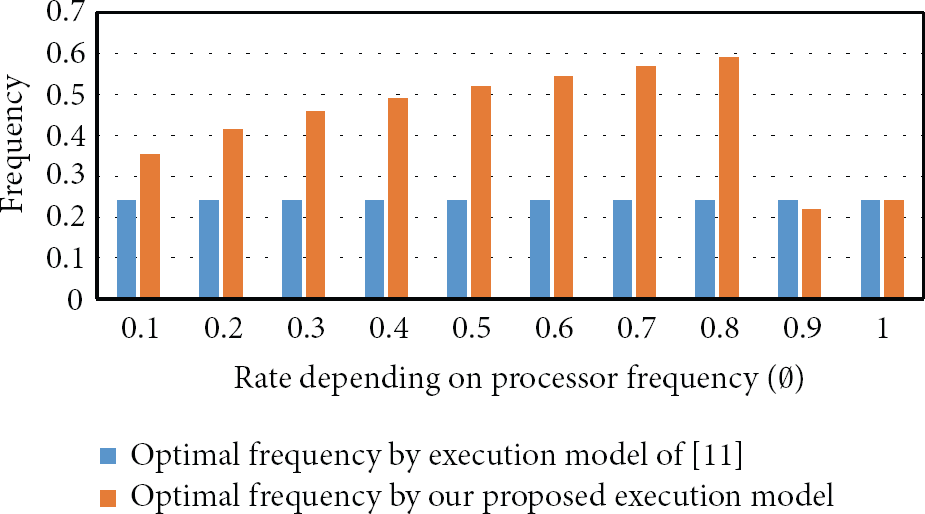

This simulation results in Figure 5 show that our algorithm enables better power management than the previous approach [11]. This is because our algorithm is based on an extended model that more accurately reflects the architecture of the sensor node.

Energy consumption for various ∅.

6. Conclusion and Future Work

A sensor node employs various devices, including a microcontroller unit for processing, a radio frequency unit for transmissions, a battery to supply power, and multiple sensor units for sensing. Some of these devices depend directly on the clock frequency and others do not.

In this study, we proposed an extended model that considers the case in which the execution time of the task is not determined only by the clock frequency of the processor.

Based on the proposed model, we presented an algorithm that calculates the optimal clock frequency of the processor to achieve system-wide energy savings. We validated our approach by both analysis and simulation results in various scenarios.

In future work, we shall extend the model to handle multiple devices; we also intend to perform experiments with actual sensor nodes.

Footnotes

Conflict of Interests

The authors declare that there is no conflict of interests regarding the publication of this paper.

Acknowledgments

This research was supported by the Chung-Ang University Excellent Student Scholarship, the National Research Foundation (NRF-2011-0013924), and the MSIP (Ministry of Science, ICT, and Future Planning) under the ITRC (Information Technology Research Center) support program (NIPA-2014-H0301-14-1023) supervised by the NIPA.