Abstract

The low-cost crystal oscillators in wireless sensor networks are prone to be affected by their working conditions such as voltage, temperature, and humidity. Such effect is often ignored by existing time synchronization solutions that typically assume the frequency error of a given node to be constant and hence adopt frequent timestamp exchanges, resulting in high energy consumptions. We propose a novel voltage-aware time synchronization (VATS) scheme that is inspired by the fact that the clock skew is highly correlated to voltage supplies. VATS features a two-phase process: (i) it first estimates the clock skew and updates the frequency error autonomously based on the local voltage level; (ii) it then adjusts the resynchronization intervals dynamically according to a given synchronization error controlling factor and the synchronization error accumulating rate to balance the calibration accuracy and cost. Since VATS leverages voltage measurements to assist clock skew estimation, it does not require frequent timestamp exchanges as in traditional schemes. Extensive simulation results illustrate the superior performance of the proposed method in terms of calculation accuracy, robustness, and reduced timestamp exchanges for energy saving.

1. Introduction

Time synchronization is one of the most fundamental and widely employed middle-ware services in wireless sensor networks (WSNs). It enables nodes in the network to maintain a common notion of time with respect to a global reference or among themselves. Accurate time synchronization is critical to many tasks in various WSN applications [1–3] including localization, sleep and transmission scheduling, data fusion, and cooperative transmission. However, due to the instability of the oscillator, the time reading of one node is often different from that of another node, which is termed as clock offset. An uncontrolled clock offset may severely degrade the network performance and even disrupt the normal operations of WSNs. For instance, in a WSN for wild animal tracking, the clock offset may inevitably lead to a high level of positioning and tracking errors, since the signal processing techniques, which are used to learn the animals' movements from the raw data, usually require tight time synchronization among sensor node clocks.

1.1. Existing Schemes and Their Limitations

To achieve time synchronization between nodes, traditional time synchronization protocols mainly focus on clock offset estimation and compensation that rely on timestamp exchange, including TPSN [4], RBS [5], and FTSP [6]. Underlying all these methods is an assumption that clock skew (the changing rate of clock offset) is stable and independent of the working conditions. However, this assumption is unrealistic in the WSNs. Due to the low-cost design of the oscillators, the clock skew is not stable and fluctuates with the working conditions such as voltage, temperature, and humidity, which undermines the skew estimation. The miscalculation of clock skew forces synchronization protocols to resynchronize too frequently, hence, introduces heavy communication overhead. Unfortunately, WSNs are representative example of resource-constrained networks, especially its limited power supply. As a result, the timestamp exchange based synchronization (TETS hereafter) schemes are unsuitable for the power limited WSNs. What is worse is that these schemes often conduct in a hierarchical way, which results in the accumulation of the calibration error. Such facts largely prohibit the scalability of those TETS solutions in practice.

According to the analysis on the traditional time synchronization protocol, it can be easily summarized that time synchronization in the WSNs faces the following three challenges. First, due to the low-cost design, the frequency of the oscillator fluctuates with the working condition (such as voltage and temperature); thus, the clock synchronization should be adaptive to the changing environment. Second, the power supply for sensor nodes is limited; thus, the resynchronization period should be prolonged to reduce the times of transmitting. Third, the synchronization error gets accumulated hop by hop exponentially through the hierarchical network topology, which makes the scalability of the synchronization scheme to be another quite important requirement.

To address the above issues, an emerging type of solutions has been recently proposed which makes use of the environmental information as a common reference. These schemes mainly focus on the estimation and compensation of clock skew, which is the inherent and dominant reason causing clock desynchronization. Considering the fact that the clock skew is highly correlated with the environment, so the environmental parameters can be used to assist the estimation of the clock skew. A typical example is using temperature measurement. In EACS [7], by referring to the temperature data, the scheme can indirectly obtain the instantaneous clock skew of the node. In TCTS [8], temperature is used to autonomously calibrate the local oscillator. Both of these two schemes utilize the temperature information to autonomously calibrate the clock skew, which prolongs the resynchronization period without losing synchronization precision, thus reducing the energy consumption. In addition, the error accumulation caused by the “hop by hop” communication is also mitigated since fewer message exchange is required. However, this kind of solutions still overlooks several problems. (1) Inaccurate temperature measurements may lead to an estimation error of clock skew. This problem could be mitigated by using expensive high-precision temperature sensors, which, however, would increase the cost and overhead. (2) Temperature data acquisition may introduce extra cost if the temperature information is unnecessary for the network application. (3) These schemes do not balance between synchronization accuracy and energy efficiency since they typically configure the resynchronization in a fixed-cycle fashion.

1.2. The VATS Scheme

In this paper, a novel clock synchronization scheme called VATS is proposed, which allows network nodes to estimate the clock skew by referring to the current supply voltage of the node. Our scheme is based on the following observations and facts.

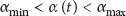

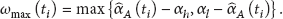

Figure 1 shows the logged frequency of the 32.768 KHz oscillator on a MICAz under different voltage value with a oscilloscope. we can see from Figure 1 that the frequency of the oscillator increased with the voltage value which rose from 2.0 V to 3.5 V. The clock skew went from 13.43 ppm (parts per million) to 15.26 ppm. For instance,

Clock frequency measurement.

Compared with the temperature measurements obtained by sensors, the voltage measurements contain considerably lower noise with a higher precision and are thus more conducive to clock skew estimation. In addition, the voltage value can be directly obtained by nodes without any extra hardware or sensor support, thus consuming less energy than EACS [7] and TCTS [8]. To provide a tradeoff between synchronization accuracy and energy efficiency, we further propose a dynamic resynchronization scheme, which can adjust the resynchronization interval dynamically based on the observed error accumulation. Our solution is generally applicable to most existing networks and is particularly suitable for networks where communication gets either lost or severely impacted, since the skew estimation largely relies on local information.

The proposed VATS approach is composed of two core phases: local time maintenance and dynamic resynchronization. These two phases both lean upon a voltage-skew relational table obtained through empirically study. The contributions of this work are summarized as follows.

We empirically study the correlation between the voltage and clock skew. Starting from a simple examining in laboratory, our measurement validates that the voltage is able to serve as a viable reference for clock skew estimation. Based on the observation of the skew-voltage experiment, we introduce a novel voltage-aware time synchronization scheme for autonomously skew estimation, which substantially improves the clock accuracy and reduces the energy consumption. We further propose a dynamic resynchronization scheme for adaptive clock calibration, which advances an important step towards system efficiency and flexibility. Simulation results illustrate the superior performance of the proposed method in terms of calculation accuracy, robustness, and reduced timestamp exchanges for energy saving.

The rest of the paper is organized as follows. Section 2 summarizes the related work. In Section 3 we introduce the preliminary information of this paper. Section 4 presents our initial empirical measurement study that motivates this work. The major design of our two-phase voltage-aware clock time synchronization protocol is given in Section 5. Section 6 shows the performance evaluation results obtained from extensive simulations. Finally, Section 7 concludes the whole paper.

2. Related work

Recent years have witnessed the emergence of many clock synchronization schemes designed for wireless sensor networks. These protocols have their own benefits, respectively, as well as limitations. Previous researches mostly focus on combating the nondeterminism along the critical path of wireless communication. RBS [5] eliminates the send and access delay by applying a receiver-receiver scheme, and it is also possible to remove the receive time uncertainty with minimal OS modifications. While TPSN [4] proposed a “pair-wise handshake” model to successfully estimate the unknown propagation delay, it, meanwhile, eliminates the same three delays as in RBS through MAC layer time-stamping scheme. FTSP [6] promotes the precision by the use of multiple MAC layer time-stamping and comprehensive error compensation. However, compared with the nondeterminism along the critical path, unstability of the oscillator frequency becomes the inherent cause for clock desynchronization and makes it unreasonable to carry out clock synchronization using existing schemes.

To tackle the problem mentioned above, the researchers shift their focus on studying the fundamentals of clock uncertain to achieve higher performance precision. Initially, constant-skew clock model [9, 10] is applied to describe the clock skew, and linear regression [4, 5, 11] is utilized to estimate the clock skew. Considering the strong assumption of constant-skew model, many designs employ the bounded skew model [12, 13] to achieve higher precision. However, clock frequency often influenced by voltage, temperature [7, 8, 14], and so forth, so constant model and bounded model are not applicable here. References [7, 14, 15] use a hybrid two-model system to describe the clock skew and tackle the model uncertainty problem with complex Kalman filtering.

On the other hand, an emerging type of solutions has been recently proposed, which makes use of external measurement to assist skew estimation. Some of them tune to certain external signal source as common time reference. Typical examples are Wi-Fi [16], power lines [17], FM radio [18], and fluorescent lighting [19]. Other solutions, such as [7, 8], utilize the correlation between clock skew and environmental data to track the clock skew. However, most of these schemes introduce extra hardware [16–18] to capture periodical signals, or some of them need to collect environmental information [7, 8, 19], which may introduce extra overhead (in the situation that the collected environmental information is useless for the application). Reference [14] takes voltage into consideration when estimating clock skew; however, it fails to work out the correlation between clock skew and the voltage.

Different from the aforementioned schemes, our design explores the voltage supply compensated scheme to estimate the clock skew. The voltage value can be straightforwardly gained by nodes without any extra hardware or sensors support, which distinctly reduces the energy consumption. In addition, the voltage data contain considerably lower noise than the environmental data measurement.

3. Preliminary

For presentation clarity, we first define the important terms we use to describe clock behavior in this paper.

3.1. Clock Offset versus Clock Skew

Clock. The device used to measure time is called clock. Clock consists of a periodic signal source and a counter to record the number of periods from a starting point. We denote the reading of clock A at real time t as

Clock Offset. Due to the combination of factors in fabrication and the working environment, the periodic signal of different clocks output frequencies with small offsets from the desired value. As a result, the clock reading is different from the real value. Clock offset is used to describe the difference between the reading of two or more different nodes. We denote the clock offset of clock A relative to clock B at real time t is as

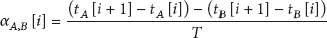

Clock Skew. It is the slope of the change in clock offset, and it reflects the frequency difference of two or more different nodes, which is the inherent cause for clock desynchronization. We denote the clock skew of clock A relative to clock B at real time t as

3.2. Skew Model

In the ideal situation, the clock offset is a constant value, which means that the clock skew is 0. However, the frequency of an oscillator fluctuates over time due to the changes in supply voltage, temperature, and so forth. The instability of clock frequency leads to the variation of clock skew. Fortunately, the clock skew is not an arbitrary value, and it can be described by different clock skew models:

Constant Skew Model. The clock skew is assumed to be constant, and the variation of the skew can be included into the processing noise, which can be considered as crystal jitter (shown in (5)). This is reasonable if the required precision is low:

Bounded Skew Model. The deviation of the clock skew from the ideal value (

Constant-Rate Skew Model. The variation of skew is assumed to be a constant rate process. We denote the changing rate of a clock skew as ρ, so the constant-rate skew model can be described as

3.3. Timestamps Exchange

Considering a simple skew estimation case with two nodes, let a node sends timestamps to the other node periodically about its local time reading. In Figure 2, we illustrate two synchronization periods. Node A sends timestamps at times

Synchronization between two nodes.

4. Empirical Measurement Study

To accurately estimate the clock skew, we first investigate its property from measurement results. The measurement focuses on evaluating the correlation between the clock skew and the voltage supply value. The clock skew is measured by the timestamps exchange as explained in Section 3.3.

4.1. Measurement Setting

We use a laptop (IBM ThinkPad-X61) as a reference device and assume that its clock reading is the real time. A node is set to send timestamps containing the voltage value at a constant internal as shown in Figure 3. The sending interval is set to one second for simplicity. Another node, which is connected to the laptop, receives the timestamps from the sender and offers an interrupt signal to the laptop as soon as the timestamp arrives. Hence, we can use these messages to obtain the clock skew measurement as discussed in Section 3.3. To avoid the buffer jitter, when a serial port event interrupt is triggered, the laptop will read the system time right away and then process the timestamp immediately.

The experimental equipment: a node for sending timestamps, a node with temperature sensor, and a stabilized voltage supply.

Since a precise control of voltage supply is required in this experiment, the node is driven by a stabilized voltage supply instead of fresh batteries. In this measurement, the voltage value is set to vary from 2.5 V to 5.5 V, with the step of 0.5 V. As we mentioned in Section 3.3, the delay along the critical path of message delivery can be considered as white Gaussian noise with the error variance

4.2. Measurement Result and Analysis

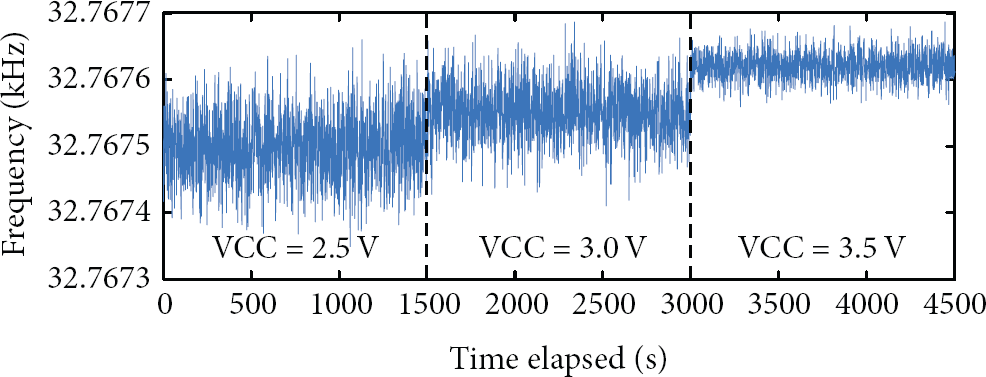

The measurement result is show in Figure 4. From the figure, we can observe that, despite the inherent clock skew of the three nodes different from each other, the clock skew of these nodes presents a similar increase tendency when the voltage decreases. For instance, as the voltage descends from 5.5 V to 2.5 V, the clock skew of node3 increases from 9.15 ppm to 15.26 ppm, which means that the clock skew of node3 increases at a speed of 2 ppm/v. In other words, the effect of the voltage change is significant and cannot be ignored. To reveal the correlation, we calculate the Pearson product moment correlation coefficient (

Experiment on voltage and clock skew. In the figure, despite the natural clock skew of the three nodes different from each other, the clock skew of these nodes presents a similar increase tendency as the voltage decrease, which is called “stair phenomenon.”

A more important observation is that, in Figure 4, the correlation between the clock skew and the corresponding voltage exhibits a characteristic “stair phenomenon.” Take, for instance, the changing style of node2. During the period when the voltage decreases from 4.5 V to 3.0 V, the change of clock skew is marginal, and the constant clock skew model discussed in Section 3.2 is compatible to describe it. However, when the voltage decreases from 5.5 V to 4.5 V, the increase of clock skew is comparatively apparent, and thus we can use the constant-rate skew model shown in Section 3.2 to characterize the change of clock skew. We refer to the period when the clock skew increases visibly as the “increase period,” and the period when the clock skew is almost constant as the “stable period.” The observed “stair phenomenon” demonstrates that the clock skew exhibits a hybrid change pattern.

In short, we summarize the conclusion as follows.

The clock skew is sensitive to the voltage supply due to the low-cost design of the oscillator; thus, the voltage supply should be taken into consideration for the clock synchronization scheme. The clock skew and the voltage are indeed highly correlated, and this correlation can be used to assist the clock skew estimation. Different clocks exhibit different clock skew change patterns with respect to voltages. Under the influence of the voltage supply, the clock skew presents multiple changing patterns.

5. Two-Phase Voltage-Aware Time Synchronization

In this section, first of all, we first introduce the basic idea of our two-phase voltage-aware time synchronization scheme (VATS) and then give details of the design.

5.1. Overview

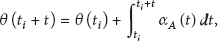

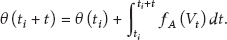

The target of VATS is to ensure local time consistent among different nodes. In Section 3, we have stated that the difference between two nodes is referred to as clock offset—the accumulation of clock skew. Clock offset evolves as

Equation (12) essentially indicated that, by continuously estimating the clock skew, the local clock can be precisely maintained. As a matter of fact, the variance of clock skew is limited within a short period of time and the voltage supply does not change very quickly during the period. Hence, instead of continuously measuring the clock skew, we compensate the local clock by using the native clock and estimated clock skew. To further guarantee the accuracy of such a prediction, we configure the clock calibration in a periodical fashion, as depicted in Figure 5.

Calibration period of VATS.

However, as unveiled in existing works [20], the clock skew and offset estimation often contain varieties of noises. These noises may lead to the accumulation of synchronization error; thus, a periodic resynchronization with the reference node by timestamps exchange is necessary. We introduce a dynamic resynchronization scheme to restrict the total amount of the synchronization error.

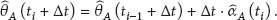

In Figure 5, we illustrate two calibration periods. During calibration 1 (blue area), the node estimates the clock skew

Overview of VATS.

5.2. Clock Skew Table

In order to compensate the clock skew autonomously, a clock skew table containing clock skew with respect to voltage for each node is required. The table is established based on the training dataset which is obtained from the measurement result in Section 4. This is conducted offline, before the deployment. As discussed in Section 4, different pairs of clocks exhibit different clock skew change patterns with respect to voltage, so the skew table stored in different nodes is independent. It is to note that, in order to retain a common time in the whole network, the table for each node must refer to the same reference.

5.3. Local Time Maintenance

Skew detection serves as the first step towards local time maintenance since the clock offset results from the accumulation of the skew. In our VATS scheme, the clock skew is estimated by using the current voltage supply value and the clock skew table. The obtained voltage of node A in the ith calibration period can be noted as

5.4. Dynamic Resynchronization Interval Adjustment Scheme

To eliminate the accumulation of synchronization error, a periodic resynchronization with the reference node by timestamp exchange is necessary. Given the resource-constrained characteristic of the WSNs, a tradeoff between accuracy and communication cost is required. We now provide a dynamic resynchronization interval adjustment scheme, in which the resynchronization interval can be controlled through the parameters μ and λ.

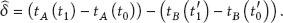

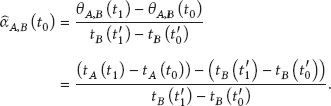

(1) Error Controlling Factor Lambda. We first introduce a synchronization error controlling factor μ to restrict the total amount of synchronization error accumulated between two resynchronizations. Suppose the error detected at the last resynchronization period in the ith timestamps exchange is

(2) Regulatory Factor Lambda. However, the abovementioned method still needs to be sophisticated. As we have discussed in Section 4, the clock exhibits multiple skew changing pattern with respect to its current voltage, and we will explain next that this phenomenon causes the error accumulating rate difference during different voltage range. Thus the resynchronization interval should also be adaptive to the multiple changing pattern of clock skew. We give the following analysis about it.

As mentioned in Section 5.3, the error introduced by skew estimation is mainly caused by the linear approximation which we used when the table entry is missing. Thus, we have

Error analysis of the “table look-up.” The estimated value is marked as the blue solid line, and the true value is marked as the blue dashed line.

Figure 7 shows the variation trend of the clock skew of node3 related to the changing voltage with a variation range from 5.5 V to 2.5 V. We take the change between 5.0 V and 4.5 V, for instance, to explain the effect of the changing rate of clock skew on

λ

in Stable Period. The clock skew increases sluggishly in stable duration. Thus the synchronization error introduced by linear approximation is considered negligible compared with the increase duration. We set

λ

in Increase Period. Since the clock skew increases rapidly in this duration, the synchronization error introduced by linear approximation is considerably larger. Thus we set that

In simple terms, we can summarize the following.

The parameter μ can be seen as the required precision, which is used to restrict the unbounded accumulation of synchronization error. The parameter λ is set to adjust the resynchronization interval, in order that the resynchronization interval is adaptive to the multiple changing pattern of the clock skew.

We list operations in our VATS scheme as Algorithm 1.

(1) (2) (3) μ: The re-synchronization threshold (4) N: The number of periods (5) τ: local clock tick unit (6) (7) Initialize the clock offset (8) Initialize the synchronization error (9) (10) In Phase I: Local time maintenance; (11) Obtain the current voltage supply (12) (13) (14) (15) In (16) (17) (18) (19) (20) (21) (22) (23) In Phase II: Dynamic interval adjustment; (24) (25) Exchange timedtamps with reference node; (26) (27) (28) (29) (30) (31) Set the next re-synchronization interval as (32) (33)

The code between lines 10–22 describes the local time maintenance phase, which estimates the clock skew and the offset and then compensates the local clock. The code between lines 23–37 describes the dynamic resynchronization phase.

Discussions. To address the challenges of time synchronization in WSNs, first, the clock skew estimation is referring to the nodes' current voltage supply value in VATS; thus, the effect of voltage supply change is removed. Second, the clock skew is compensated appropriately, so the resynchronization period can be substantially prolonged. Given that the communication energy accounts for a major proportion of the energy consumption in WSNs, using our VATS scheme, the overall energy consumption is much less. Third, since our VATS scheme is independent of the network message exchange, time synchronization can be retained even when the network is temporarily disconnected. Such characteristics particularly suit various mobility-enabled scenarios. Besides, this characteristic removes the error accumulation caused by “hop by hop” timestamps exchange.

6. Performance Evaluation and Discussion

Extensive simulations have been conducted to evaluate the performance of VATS. The simulations focus on verifying the following three properties: (i) accurate skew estimation, (ii) robustness, and (iii) long resynchronization period.

6.1. Simulation Setting

We generate the simulation data based on the measurement results of node1, node2, and node3 in Section 4. In the simulation, the voltage varied from 3.5 V to 2.5 V as shown in Figure 8. The corresponding clock skew of the three nodes varied from 13.43 ppm to 15.26 ppm, 36.62 ppm to 39.06 ppm, and 24.42 ppm to 25.94 ppm, respectively, according to the measurement result. The measurement noises followed a Gaussian distribution. We used a set of training data to obtain the table of clock skew compensation with respect to voltage.

The changing voltage supply value, which simulates the power depletion of the fresh batteries.

The reason why we choose the interval of 3.5 V to 2.5 V is that the skew change pattern of the three nodes in this interval is diverse from each other. Thus the difference of clock skew estimation accuracy in different skew change pattern can be observed.

6.2. Accuracy

One of the main advantages of our VATS scheme is that it exploits the relationship of clock skew and voltage to estimate and calibrate the clock skew, which guarantees the skew estimation precision during the resynchronization interval.

Figure 9 shows the skew estimation result of the three nodes. From the figure, we can observe that the estimation results (the red line) of the three nodes are all close to the real values (the yellow line), even though the clock measurements (the dots) contain severe noise. This is because we can estimate the clock skew using voltage estimation, so the negative impact of voltage change is minimized. From the figure, the estimation errors are obvious during partial stage. For node1, during the period that the voltage changes from 3.2 V to 3 V (2000 to 2800 (100 s)), the estimation error appears to be more obvious than other periods. For node3, the estimation error increases during the period that the voltage changes from 3 V to 2.5 V. It is remarkable since the change in estimation error during this period is markedly compared to the period that the voltage changes from 3.5 V to 3 V, during which the estimation results and the real values coincide with each other.

The clock skew estimation performance. We can clearly see that the estimation results of the three nodes are all close to the real values even though the clock measurements contain severe noise. The performance of VATS is extremely high.

To further evaluate the estimation error, the square error of the three nodes is shown in Figure 10. The result shows that, despite the accuracy of the three nodes gap big (it is caused by fabrication process or other individual factors), the tendency of the accuracy has the common obvious temporality, which is consistent with the estimation results and the real values shown in Figure 9. The sudden increase of the estimation error is considered prompted by the speed increases of clock skew, which is explained in Section 5.4. From Figure 4, we can observe that, for node3, the clock skew accelerates from 3 V to 3.5 V; as a result, Figure 10 exhibits a sudden error increase during 3000 to 3400 (100 s) of node3. The other two nodes exhibit the same pattern. The sudden increase of skew estimation increase can be restricted by the “dynamic interval adjustment scheme” introduced in Section 5.4.

The clock skew estimation variance. The tendency of the accuracy of node1, node2, and node3 has the common obvious temporality, which is consistent with the estimation results and the real values shown in Figure 9.

From statistics, we find that the average error (the solid red line) for every 100-time slot (100 s) keeps less than

6.3. Robustness

Another advantage of VATS over the TETS schemes is in scenarios where the network is temporarily disconnected. Examples of such scenarios are atrocious environmental conditions (such as blizzard and torrential rain which may damage the antenna), mobility, or secrecy actions where radio silence is necessary. In these scenarios, VATS can still obtain the desired voltage values for clock skew estimation, and the calibration mainly relies on the voltage value. In contrast, the TETS schemes can only rely on the clock skew estimated by the last timestamp exchange.

Figure 11 compares the clock offset of VATS (the red line) with the TETS schemes (the blue line) when the network is disconnected. The result shows that, at the initial stage (0–1000 s), the performances of VATS and TETS schemes are almost parallel. However, after the voltage starts to change significantly from the initial voltage, the TETS scheme starts to lose accuracy since the gap between the current voltage and the voltage when the last clock skew estimated by the TETS scheme starts to increase, while TCTS can keep its accuracy at a very precise level. Over the 4 days where no timestamp exchange occurs, our VATS scheme only accumulates less than 0.03 s of time synchronization error.

Illustration of what happens if time synchronization is stopped. We can clearly see how TETS schemes performance worsens once the network is disconnected, whereas VATS keeps the synchronization accuracy at a much higher level.

On the other hand, we noted that the compensated clock offset is in a zigzag style as shown in the subfigure. This is because the clock offset compensation is based on the compensation threshold. Therefore, only the offset accumulated to a certain threshold can be compensated using (17) as discussed in Section 5.3.

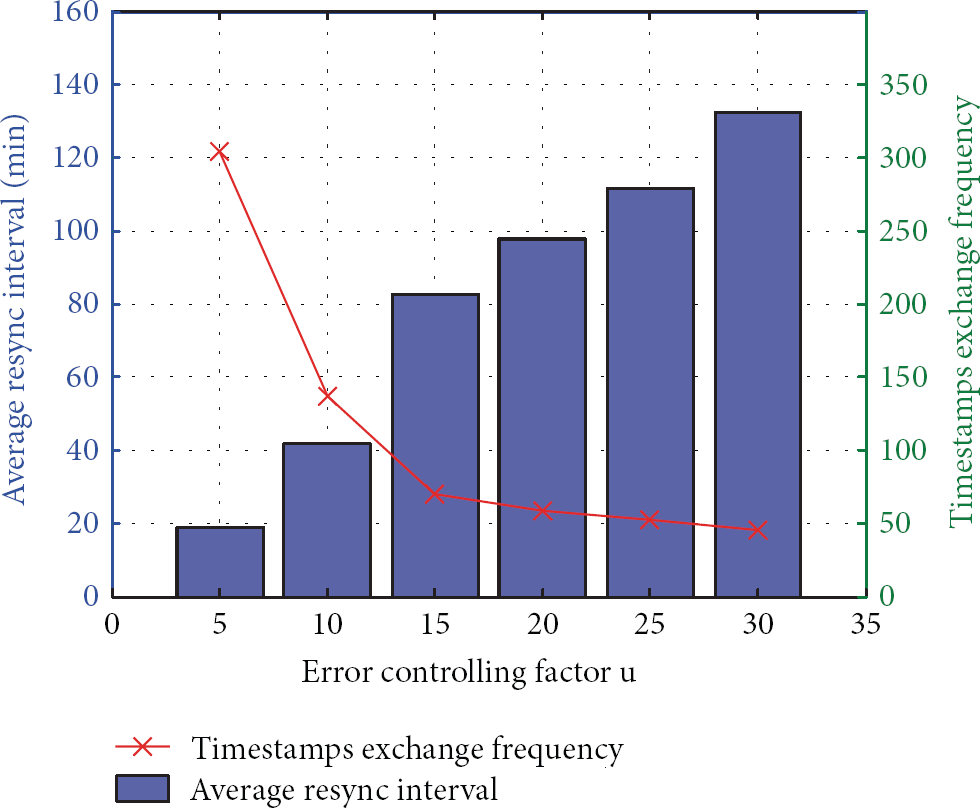

6.4. Period

To understand the resynchronization period of our VATS scheme, we evaluate the VATS under different error controlling factor μ. We choose five different error controlling factors to be 5, 10, 15, 25, and 30 native clock ticks. For each μ, the experiment lasts 96 hours. When the experiment terminates, we calculate the average length of the resynchronization interval and the timestamp exchange frequency under each controlling factor. The statistical result is shown in Figure 12. It is obvious that the average length of the resynchronization interval lengthened as the controlling factor increases; meanwhile, the timestamp exchange frequency is reduced. That is because a larger μ indicates a looser requirement of synchronization precision; thus a long resynchronization period is adequate.

This graph shows the average resynchronization interval and the timestamps exchange frequency under different error controlling factors. The resynchronization interval rapidly lengthened as the error controlling factor increased and thus save power and communication overhead.

We can also observe from the figure that the resynchronization interval is usually longer than 18 min even the error controlling factor is 5 native clock ticks, while that for TETS schemes is less than 150 s. In other words, using TATS, the synchronization communication cost is reduced by an order of magnitude, which is highly desired for power-constrained wireless sensor networks.

7. Conclusion and Further Discussion

In this paper, we have proposed a novel voltage-aware time synchronization (VATS) scheme for wireless sensor networks. The VATS scheme is based on the fact that clock skew is highly correlated to the voltage supply. By using the relationship between clock skew and voltage supply, the clock that is updated only relies on the local information before the clock resynchronization is triggered, which prolongs the resynchronization period in significant measure. This improvement achieves the overall network energy saving since fewer timestamps exchange is needed, which is significant for the power-constrained wireless sensor networks. To remove the accumulated error in skew estimation, we introduce a dynamic resynchronization. This scheme considers both the accuracy and the cost. In addition, our VATS scheme is also applicable to the scenarios where the network is temporarily disconnected which improves the robustness of the whole networks.

In this paper, we adopt a widely used assumption that the temperature or other environmental parameters are constant and in a most suitable condition. This assumption is somewhat unrealistic in some practical settings. In our future research, we will investigate the impact of other environment factors (such as temperature, humidity, electromagnetic interference, and vibration) on clock skew which are treated as noise in this work.

Footnotes

Conflict of Interests

The authors declare that there is no conflict of interests regarding the publication of this paper.

Acknowledgments

This work was supported by the Project NSFC (61070176, 61170218, 61272461, 61373177, and 61202393), the Project National Key Technology R and D Program (2013BAK01B02, 2013BAK01B05), and the Key Project of Chinese Ministry of Education 211181, International Cooperation Foundation of Shaanxi Province, China, 2013KW01-02. NSFC (61202198) and China Postdoctoral Science Foundation (Grant No. 2012M521797).